|

2.6V至6.5V输入电源VGON和VGOFF的线性调节器控制器CXSU63137电流模式升压调节器大电流运算放大器 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

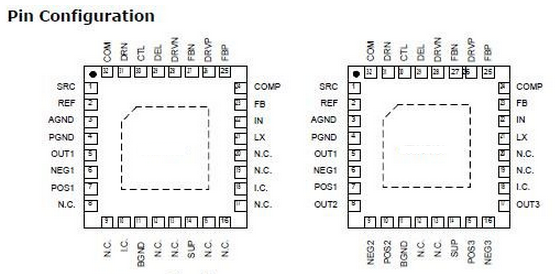

目录 1.产品概述 2.产品特点 一,产品概述(General Description) The CXSU63137 integrates with a high-performance step-up converter, two linear-regulator controllers, a high voltage switch and one (CXSU63137), three (CXSU63137) or five (CXSU63137) high current operational amplifiers for TFT-LCD applications.The main step-up regulator is a current-mode, fixed-fre-quency PWM switching regulator. The 1.2MHz switching frequency allows the usage of low-profile inductors and ceramic capacitors to minimize the thickness of LCD panel designs. · 2.6V to 6.5V Input Supply Range · Current-Mode Step-Up Regulator - Fast Transient Response - 1.2MHz Fixed Operating Frequency · ±1.5% High-Accuracy Output Voltage · 3A, 20V, 0.25W Internal N-Channel MOSFET · High Efficiency · Low Quiescent Current (0.6mA Typical) · Linear-Regulator Controllers for VGON and VGOFF · High-performance Operational Amplifiers - ±150mA Output Short-Circuit Current - 13V/ms Slew Rate - 10MHz, -3dB Bandwidth - Rail-to-Rail Inputs/Outputs · Fault-Delay Timer and Fault Latch for All Regulator Outputs · Over-Temperature Protection · Available in Compact 32-pin 5mmx5mm Thin QFN Package (TQFN5x5-32) · Lead Free Available (RoHS Compliant) 三,应用范围 (Applications) TFT LCD Displays for Monitors 需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持! 五,产品封装图 (Package)

PinFunction Description

六.电路原理图

发表评论

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

发表时间:2020-06-08浏览次数:191

| 最新信息 |

|---|

| 热门信息 |

|---|

| 推荐信息 |

|---|

| 头条信息 |

|---|

Pin Function Description

Pin Function Description